深入理解时钟发生器原理及其在高性能计算中的作用

深入理解时钟发生器原理及其在高性能计算中的作用

在高性能计算(HPC)系统中,时钟发生器不仅是时间基准的提供者,更是系统性能优化的关键因素。从超级计算机到人工智能加速卡,时钟质量直接决定并行处理能力、数据吞吐率与系统可靠性。

一、时钟发生器的核心技术指标

评估一个时钟发生器的优劣,主要关注以下几个参数:

- 频率范围:支持从几十MHz到超过10GHz的可调输出,适应不同芯片需求。

- 相位抖动(Jitter):越低越好,通常要求低于100ps RMS,避免误码率上升。

- 频率稳定性:受温度、电压、老化影响小,长期保持精度。

- 多通道输出能力:支持多个独立时钟输出,满足多核、多模块同步需求。

二、时钟发生器在高性能计算中的关键角色

在高性能计算系统中,时钟发生器承担着三大核心任务:

- 全局同步:确保所有处理器核心、内存控制器、I/O接口在同一时间基准下运行,防止数据竞争与错序。

- 低延迟时钟分配:采用差分时钟(如LVDS、HCSL)和星型拓扑布线,减少时钟偏移(Skew)。

- 动态频率调节支持:配合电源管理单元(PMU),实现按需调频(DVFS),在性能与功耗间取得平衡。

三、先进时钟发生器架构示例

当前主流的高性能时钟发生器采用“多级锁相环”结构,例如:

- 双环锁相环(Dual-Loop PLL):外环负责粗调频率,内环负责精细调节,有效降低抖动。

- 数字锁相环(DPLL):利用数字信号处理算法进行相位校准,抗干扰能力强。

- 时钟合成器(Clock Synthesizer):集成多个时钟源与分频逻辑,实现单芯片多频输出。

四、实际案例分析:AI训练加速卡中的时钟设计

以英伟达A100 GPU为例,其内部集成了复杂的时钟树结构。外部时钟发生器提供100MHz参考时钟,经内部多级PLL倍频至数百MHz,并通过专用时钟路由网络分配至矩阵运算单元、内存子系统与互联总线。该设计确保了每秒数十万亿次浮点运算的同步执行,极大提升了训练效率。

五、未来展望

随着摩尔定律放缓,系统性能提升更多依赖于架构优化与时钟管理创新。未来的时钟发生器将融合人工智能算法,实现自适应时钟调度;同时,光子时钟、量子时钟等前沿技术也可能逐步进入实用阶段,开启全新纪元。

- 深入理解时钟发生器原理及其在高性能计算中的作用

- 深入理解时钟发生器原理及其在嵌入式系统中的关键作用

- 时钟发生器在高性能计算系统中的关键作用

- 时钟发生器在高性能计算系统中的作用与优化策略

- 时钟发生器在高性能计算中的关键角色分析

- MEMS时钟发生器在高端通信与AI边缘计算中的关键作用

- 深入解析时钟发生器的工作原理与应用领域

- 深入解析时钟发生器在高速数字系统中的关键作用

- 深入解析时钟发生器芯片的工作原理与应用优势

- 时钟发生器与时钟管理:构建高性能数字系统的基石

- 时钟发生器工作原理及应用

- 深入理解时钟发生器的性能指标与选型要点

- 时钟发生器工作原理

- 时钟发生器:原理、应用与设计

- 时钟发生器的工作原理与应用详解

- 时钟发生器的工作原理与应用解析

- 时钟发生器:原理、应用与设计考虑

- 深入解析可编程时钟发生器在高速通信系统中的应用与优势

- 时钟信号器件在高性能计算中的关键角色

- 时钟发生器的工作原理与应用领域

-

如何选择合适的时钟信号器件以优化系统性能

选型关键因素分析在设计高性能电子系统时,正确选择时钟信号器件至关重要。不当的选型可能导致系统不稳定、功耗过高甚至功能失效...

-

深入解析时钟信号器件的工作原理与应用场景

时钟信号器件的核心作用时钟信号器件是现代电子系统中不可或缺的关键组件,主要用于提供精确的时间基准信号,确保数字电路中的数...

-

贴片晶振是否优于普通晶振?深度解析性能差异

贴片晶振与普通晶振性能对比:谁更胜一筹?在现代电子设计中,贴片晶振因其小巧、高效、易于自动化组装,逐渐取代传统普通晶振。...

-

晶振、普通晶振与贴片晶振如何选择?全面对比分析

晶振、普通晶振与贴片晶振的区别与选择指南在电子设备设计中,晶振(晶体振荡器)是实现精准时钟信号的核心元件。随着技术的发展...

-

高频振荡电感型接近开关的感应头设计与实际应用案例

二、感应头结构设计及其对性能的影响感应头作为高频振荡电感型接近开关的前端感知部件,直接影响检测距离、灵敏度和环境适应性。...

-

振荡器工作原理

振荡器是一种能够产生周期性信号的电子设备或电路,其核心功能是将直流电转换为交流电。振荡器的工作原理基于正反馈机制,通过将...

-

晶振工作原理及应用

晶振,即晶体振荡器,是一种利用石英晶体(也可能是其它压电材料)的压电效应来产生稳定频率信号的电子元件。在电子设备中,晶振...

-

时钟信号器件在电子系统中的应用

时钟信号器件在电子系统中扮演着至关重要的角色,尤其是在数字电路和通信系统中。它们为电子设备提供了一个精确的时间基准,使得...

-

时钟发生器工作原理

时钟发生器是一种电子设备,其主要功能是生成稳定且精确的时钟信号,这些信号被广泛应用于各种电子设备中,包括计算机、通信设备...

-

仪表配件常见类型及功能

仪表配件在工业自动化和测量领域扮演着至关重要的角色,它们用于确保仪表系统的精确性和可靠性。常见的仪表配件包括但不限于压力...

-

谐振器工作原理及应用

谐振器是一种能够在一个或多个频率上增强信号强度的装置,它在电子、机械和光学等多个领域都有广泛的应用。谐振器的工作原理基于...

-

TQS6M4003型号部件的概述与信息查询方法

TQS6M4003 看起来像是一个型号或部件编号。在没有更多上下文的情况下,很难提供具体信息。不过,通常这种编号用于标识电子产品或部件...

-

“智”驭时间,循环定时开关:生活便捷与节能的双重守护者

在现代生活中,随着科技的不断进步,自动化设备已经渗透到我们日常的方方面面,极大地提升了生活的便利性和舒适度。其中,循环定...

-

M27*001-12F6:产品型号或部件编号的解释

M27*001-12F6 看起来像是一个产品型号或者部件编号。这样的编号通常用于标识特定的产品或组件,以便在制造、销售、维修或库存管理中快...

-

N490SH26:一个多用途的产品型号或部件编号解析

N490SH26 似乎是一个特定的型号或部件编号,但仅凭这个编号本身,没有更多的上下文信息,很难确定它确切的含义或用途。如果这是一个...

-

ABS05-32.768KHZ-T 晶体振荡器:高精度时钟信号的关键组件

ABS05-32.768KHZ-T 是一种小型的晶体振荡器,它广泛应用于电子设备中,用于提供稳定的时钟信号。这种晶体振荡器以其高精度和低功耗而受...

-

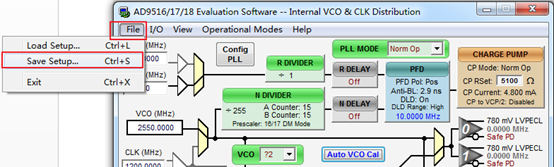

AD9517-4ABCPZ:一款高性能多功能时钟发生器的全面解析

AD9517-4ABCPZ是一款高性能的时钟发生器,广泛应用于需要精确时钟信号的各种电子系统中。这款时钟发生器具备多种功能,包括频率合成、...